高速串行總線的普及����,使得PCB板上差分信號越來越多���,那么�,PCB設計如何進行差分布線呢��?接下來專業(yè)PCB設計公司-深圳宏力捷電子為大家介紹下。

PCB設計差分布線要求

各類差分線的阻抗要求不同���,根據(jù)PCB設計要求,通過阻抗計算軟件計算出差分阻抗和對應的線寬間距��,并設置到約束管理器���。 差分線通過互相耦合來減少共模干擾�����,在條件許可的情況下盡可能平行布線����,兩根線中間不能有過孔或其他信號��。為減少損耗����,高速差分線換層時可以在換層孔的附近添加地過孔。

PCB設計差分布線操作技巧

1���、激活布線的指令�,選擇Route→connect命令,再選中已經(jīng)定義好的差分信號線�,此時已經(jīng)定義好的差分線會同時被拉出。

2����、支持單線的走線模式,當局部布線需要用單線走線模式時�,在布線命令狀態(tài)下單擊鼠標右鍵,在彈出的快捷菜單中選擇

Single Trace Mode命令模式�。

3、在布局小空間的位置差分布線時�����,可以切換至Neck Mode模式�����,同樣是在布線指令狀態(tài)下單擊鼠標右鍵����,在彈出的快捷菜單中選擇Neck Mode命令。

4����、根據(jù)布線需求選擇合適的差分過孔模式�。在布線指令狀態(tài)下單擊鼠標右鍵�����,在彈出的快捷菜單中選擇Via Pattern命令��。

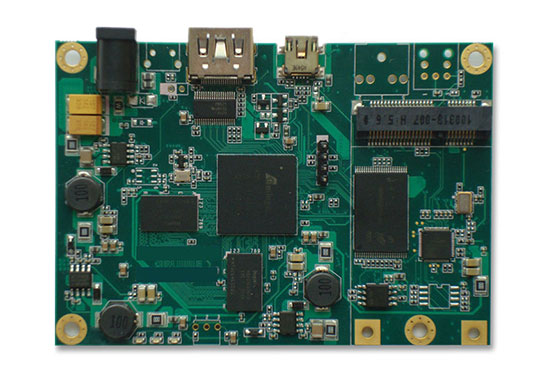

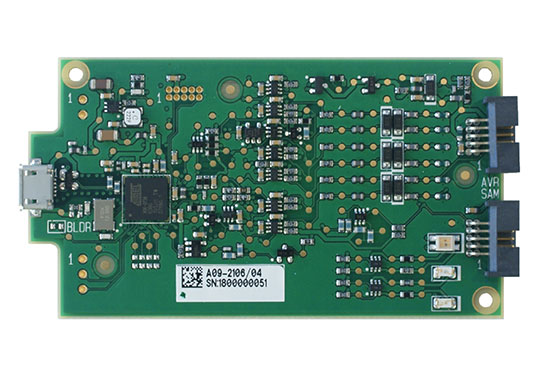

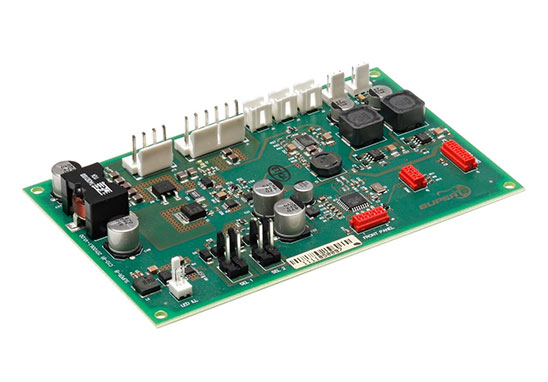

深圳宏力捷設計能力

最高信號設計速率:10Gbps CML差分信號���;

最高PCB設計層數(shù):40層;

最小線寬:2.4mil�;

最小線間距:2.4mil;

最小BGA PIN 間距:0.4mm��;

最小機械孔直徑:6mil�;

最小激光鉆孔直徑:4mil;

最大PIN數(shù)目:�����;63000+

最大元件數(shù)目:3600�;

最多BGA數(shù)目:48+。

PCB設計服務流程

1. 客戶提供原理圖咨詢PCB設計����;

2. 根據(jù)原理圖以及客戶設計要求評估報價�����;

3. 客戶確認報價�����,簽訂合同���,預付項目定金;

4. 收到預付款����,安排工程師設計;

5. 設計完成后����,提供文件截圖給客戶確認;

6. 客戶確認OK����,結清余款,提供PCB設計資料��。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料